Before going to repetition operators, first understand about the types of clock delays we use while writing our various assertions.

Simple Operator Clock Delays:

1. ## : represents cycle delay (or rather no of sampling edges)

2. ##n – specifies “n” clock cycles

3. ##0 – represents same clock cycle – overlapping signals

4. ## [min:max] – Specifies a range of clock cycles, where min and mux must be 0 or greater. $ specifies infinite number of cycles.

sequence val_ready_sequence;

valid ##1 ready;

endsequenceThis sequence tells that once valid is high, ready must be asserted 1 clock cycle later.

sequence req_grant_sequence;

req ##[2:$] grant;

endsequence

Here once the req signal is true, the grant should be high in between 2 clock cycles and at any time before simulation ends.

1. Repetition Operator: [*n]

The [*n] operator specifies that an event or condition must occur for exactly n consecutive clock cycles. This is particularly useful in timing-critical designs where sequential occurrences must align precisely.

a ##1 b [*3] ##1 c // Equiv. to a ##1 b ##1 b ##1 b ##1 c Example

This assertion ensures that when a start signal is high, a ready signal must remain high for exactly 3 consecutive clock cycles.

module repetition_assertion_example (

input logic clk,

input logic reset_n,

input logic start,

input logic ready

);

// Assertion block

property check_ready_repeats;

@(posedge clk) disable iff (!reset_n)

start |=> ready[*3]; // `ready` must be high for exactly 3 cycles after 'start' is high

endproperty

// Bind the property to an assertion

assert property (check_ready_repeats)

else $error("Assertion failed: 'ready' was not high for exactly 3 consecutive cycles after 'start'!");

endmoduleProperty:

@(posedge clk): Evaluates on the positive edge of the clock.disable iff (!reset_n): Disables the assertion when the reset is active.start |=> ready[*3]: Ensuresreadystays high for exactly 3 cycles afterstartis high.

Assertion:

- If the condition fails,

$error is triggered and $error message will be displayed.

Waveform

Here start is high at 15ns and after one clk cycle ready stays high for exactly 3 clk cycles. Assertion got passed but when start is high at second time, ready stays high only for 2 clk cycles and assertion fails.

2. Non-Consecutive Repetition Operator: [=n]

The [=n] operator allows for an event or condition to occur n times in total, but not necessarily consecutively. This is useful when events are spaced apart and continuity is not required. Also it does not require that the last match on the signal repetition happen in the clock cycle before the end the entire sequence matching.

property p1;

@(posedge clk) disable iff (rst)

start |-> data[=3] |-> stop;

endpropertyIn the above example, when the ‘start’ becomes high, the ‘data’ should be high continuously or intermittently for 3 clock cycles, followed by signal ‘stop’ to be high in any cycle after that while ‘data’ signal can remain low.

Example

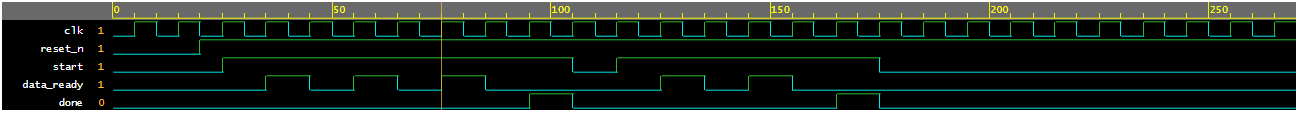

The module ensures that during a period when the start signal is high, the data_ready signal must be high exactly 3 times before done is asserted.

module non_consecutive_repetition_example (

input logic clk,

input logic reset_n,

input logic start,

input logic data_ready,

input logic done

);

// Assertion block

property check_data_ready_occurrences;

@(posedge clk) disable iff (!reset_n)

start ##1 (data_ready [=3]) ##1 done; // `data_ready` must be true exactly 3 times before `done` but not mandatory to consecutive cycles

endproperty

// Bind the property to an assertion

assert property (check_data_ready_occurrences)

else $error("Assertion failed: 'data_ready' did not occur exactly 3 times before 'done'!");

endmoduleProperty:

@(posedge clk): Evaluates on the positive edge of the clock.disable iff (!reset_n): Disables the assertion when the reset is active.start ##1 (data_ready [=3]) ##1 done: Specifies that:- After

start, there must be 3 occurrences ofdata_ready(not necessarily consecutive). - Afterward,

donemust be asserted.

- After

Assertion:

- The assertion ensures that

data_readyis high exactly 3 times beforedone. If this condition is not met,$erroris triggered.

Waveform

3. Go-To Repetition Operator: [->n]

This operator is similar to non-consecutive repetition operator. It allows the user to specify that an expression will match the number of times specified not necessarily on continuous clock cycles. The matches can be intermittent. The main requirement of a “go to” repeat is that the last match on the expression checked for repetition should happen in the clock cycle before the end of the entire sequence matching.

Example

property p1;

@(posedge clk) disable iff (rst)

start |-> data[->3] |-> stop;

endpropertyIn the above example, when the ‘start’ becomes high, the ‘data’ should be high continuously or intermittently for 3 clock cycles, followed by signal ‘stop’ to be high just after that. The third repetition of ‘data’ is required just before the success of ‘stop’.