DDR4 SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory) is a widely used memory standard in modern computing systems due to its high performance, low power consumption, and large storage capacity. It is essential in devices ranging from personal computers to servers, graphics cards, and embedded systems. This article delves into the structure of DDR4, how read and write operations work, the role of refreshing, precharge commands, timing parameters, and the function of sense amplifiers.

Structure of DDR4 SDRAM

The internal structure of DDR4 SDRAM is highly organized, designed to allow efficient access to large amounts of memory at high speeds. Below are the key components and concepts:

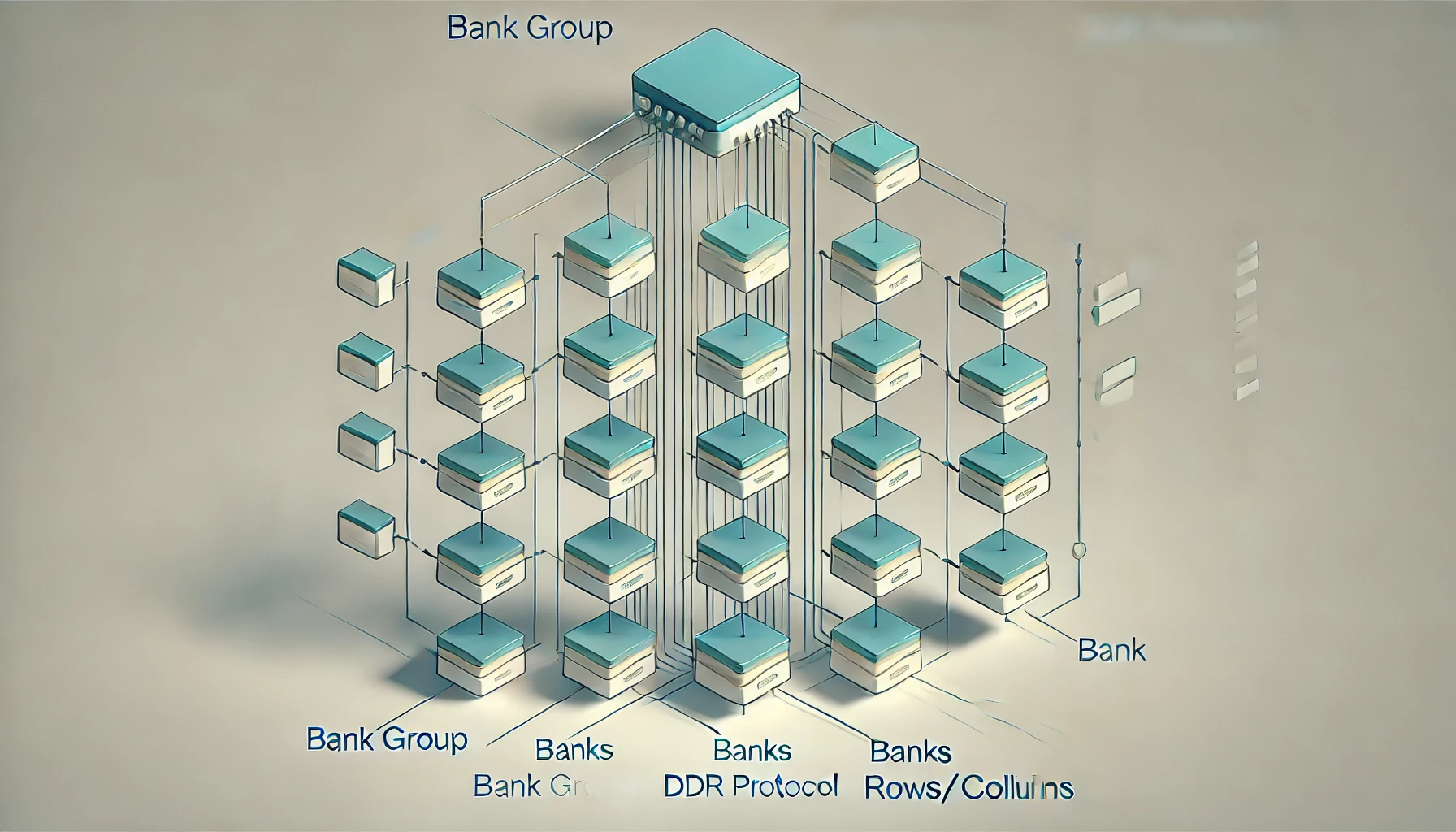

1. Bank Groups and Banks

- Bank Groups: DDR4 introduces bank groups to enhance parallelism and reduce latency. A DDR4 device typically contains multiple bank groups, each containing several banks. For example, a DDR4 device may have 4 bank groups, each with 4 banks, totaling 16 banks.

- Banks: A bank is a two-dimensional array of memory cells organized in rows and columns. Each bank can be accessed independently, allowing for parallel operations within the memory.

2. Rows and Columns

- Rows: Each bank contains a large number of rows, each storing multiple bits of data. A row address is used to select a specific row during operations.

- Columns: Once a row is activated, data can be accessed from specific columns within that row using a column address.

- Together, the row and column addresses define the location of a specific data word in memory.

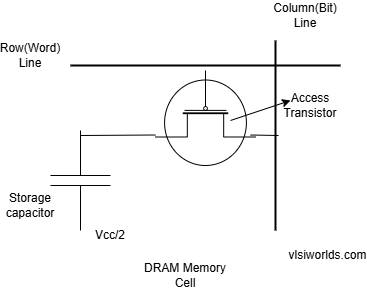

3. Bit Lines and Word Lines

- Bit Line: A bit line connects memory cells vertically in a column. It carries the charge from a memory cell to the sense amplifier for read operations or delivers charge to the cell during write operations.

- Word Line: A word line connects memory cells horizontally in a row. Activating a word line enables all the cells in the row to connect to their respective bit lines.

4. Data Organization

DDR4 is organized in a hierarchy:

- A rank consists of multiple chips (ICs), where each chip stores part of the total data.

- Each chip is divided into banks, rows, and columns.

Basic Read and Write Operations in DDR4

1. Read Operation

- Row Activation:

- Before a read operation, a row must be activated using the Activate (ACT) command.

- The memory controller sends the row address to activate the desired row. The word line corresponding to the row address is enabled, connecting the cells in the row to the bit lines.

- Data from the selected row is temporarily stored in the sense amplifiers.

- Column Access:

- After activation, a Read (RD) command is issued, specifying the column address.

- Data from the selected column is read out from the sense amplifiers and sent to the output pins.

- Precharge:

- Once the read is complete, the Precharge (PRE) command is issued to close the row and disconnect the word line, preparing the bank for the next operation.

2. Write Operation

- Row Activation:

- Similar to a read, a row must be activated first using the Activate (ACT) command.

- Column Access:

- A Write (WR) command is issued, specifying the column address and the data to be written.

- The data is stored temporarily in the sense amplifiers and then written into the memory cells through the bit lines.

- Precharge:

- The Precharge (PRE) command closes the row and prepares the bank for subsequent operations.

Refreshing and Precharge Commands

1. Refresh Command

- Why Refresh is Needed:

DDR4 SDRAM is volatile memory, and the charge stored in its cells gradually leaks over time. To prevent data loss, the memory controller periodically issues a Refresh (REF) command to restore the charge in the cells. - Types of Refresh:

- Auto-Refresh: Automatically triggered by the memory controller at regular intervals.

- Self-Refresh: A low-power mode where the memory refreshes itself without external commands, used during idle periods.

- Refresh Timing:

Refresh commands must be issued frequently (e.g., every 64 ms for all cells) to ensure data integrity.

2. Precharge Command

- The Precharge (PRE) command is used to close the currently active row in a bank, disconnecting the word line and preparing the bank for the next row activation.

- Why Precharge is Important:

Memory cells cannot be accessed if a previous row remains active. The Precharge command ensures that the bank is in a neutral state, ready for the next operation.

Timing Parameters in DDR4

DDR4 operations are governed by strict timing parameters that ensure reliable data access and prevent conflicts. Below are key timing parameters:

- tRCD (Row-to-Column Delay):

- Time between the ACT command and the RD/WR command.

- tCAS (Column Access Strobe) / CL (CAS Latency):

- Time between the RD command and the first data being available at the output.

- tRP (Row Precharge Time):

- Time required to close a row using the PRE command.

- tRAS (Row Active Time):

- Minimum time a row must remain active after an ACT command before it can be closed.

- tRC (Row Cycle Time):

- Total time for one complete row cycle, including activation, read/write, and precharge.

- tREFI (Refresh Interval):

- Maximum time between two consecutive refreshes.

- tRRD_S (Row to row delay short):

- The minimum time required between two consecutive

ACTIVATEcommands issued to rows in banks of the different bank group. Typically shorter thantRRD_L, as activating rows in the different bank group is faster.

- The minimum time required between two consecutive

- tRRD_L (Row to row delay long):

- The minimum time required between two consecutive

ACTIVATEcommands issued to rows in different banks in same bank group.

- The minimum time required between two consecutive

Sense Amplifier in DDR4

Role of the Sense Amplifier:

A sense amplifier is a circuit used in DDR4 to detect and amplify the small charge stored in a memory cell. During a read operation:

- The selected word line activates a row of memory cells.

- The small charge in each cell is transferred to the corresponding bit line.

- The sense amplifier detects the voltage difference between the bit line and its complement and amplifies it to a full logic level (either 0 or 1).

Why is the Sense Amplifier Important?

- DRAM cells store data as a small charge, which can be difficult to detect directly. The sense amplifier ensures reliable data retrieval.

- During a read operation, the sense amplifier temporarily stores the data, allowing the same row to be accessed multiple times without reactivating it.

Conclusion

DDR4 SDRAM is a highly organized and efficient memory standard that underpins modern computing systems. Understanding its structure, operations, and key components—such as banks, rows, columns, timing parameters, and sense amplifiers—is crucial for designing and verifying systems that use DDR4.