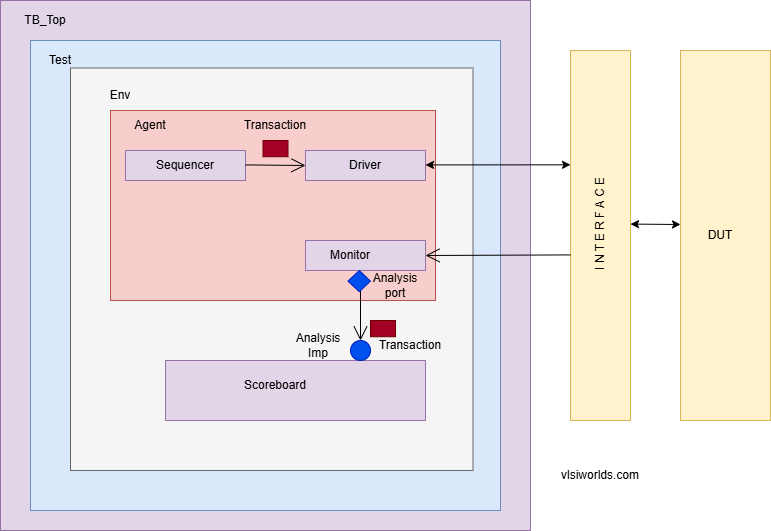

The testbench top is the highest-level component in a UVM testbench. It is responsible for instantiating and connecting all the major verification components, ensuring the DUT (Design Under Test) is properly stimulated and monitored.

The testbench top typically resides in the testbench module and interacts with the simulation environment, providing an interface to the DUT and managing simulation execution.

Key Components of the UVM Testbench Top

The UVM testbench top usually contains the following key components:

1. DUT (Design Under Test) Instance

The DUT is the hardware design that needs to be verified. It is instantiated in the testbench top and connected to the necessary verification components.

2. Virtual Interface

UVM does not allow direct access to signals. Instead, a virtual interface is used to bridge the gap between the testbench and the DUT, allowing the driver and monitor components to interact with the DUT signals.

3. UVM Test (test)

The UVM test is the highest-level component that controls the simulation flow. It configures the environment, sets up the stimulus, and manages execution. The test is usually defined separately, but the testbench top provides the necessary hooks for it. run_test() method is defined in this step.

4. Clock and Reset Generation

To ensure proper operation, the testbench top generates clock and reset signals for the DUT. These signals are typically driven by a simple SystemVerilog process.

5. Configuration Database Setup

The testbench top sets up the UVM configuration database, allowing various components to access necessary parameters such as timeouts, transaction parameters, and interface handles.

6. Top-Level Connections

It connects the DUT with the UVM environment by mapping virtual interfaces and ensuring proper signal connections.

Typical Structure of a UVM Testbench Top

Here’s a simplified representation of how a UVM testbench top might look in UVM:

module tb_top;

// Clock and reset signals

logic clk;

logic rst_n;

// Virtual interface declaration

vif vif_inst;

// DUT instance

dut u_dut (

.clk(clk),

.rst_n(rst_n),

.if(vif_inst) // Connecting the virtual interface

);

// UVM testbench environment

initial begin

// Generate clock

forever #5 clk = ~clk;

end

// Generate reset

initial begin

rst_n = 0;

#20 rst_n = 1;

end

// Start UVM test

initial begin

uvm_config_db#(virtual vif)::set(null, "*", "vif", vif_inst);

run_test("my_uvm_test");

end

//waveform generation

initial begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule