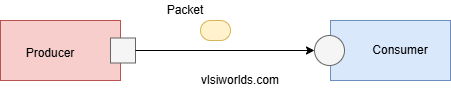

Transaction Level Modeling (TLM) is a communication mechanism where data is transferred as transactions (objects) instead of individual signals.

In UVM, a transaction is usually a sequence item that contains multiple fields such as address, data, control bits, etc.

Without TLM (Signal Level)

- Too many signals

- Tight coupling between components

- Poor reusability

With TLM (Transaction Level)

- Fewer connections

- Loose coupling

- Clean and reusable architecture

Why Do We Need TLM?

TLM helps to:

- Simplify communication between UVM components

- Separate data generation, driving, and checking

- Enable scalable and maintainable testbenches

- Improve simulation performance

All modern UVM environments use TLM-based communication.

Basic TLM Building Blocks in UVM

TLM communication uses five basic elements:

- Port – Initiates a transaction

- Export – Forwards a transaction

- Implementation (imp) – Implements the actual method

- TLM FIFOs

- Set Of Methods

What is TLM-1 in UVM?

TLM-1 provides simple, method-based communication between components using function and task calls.

It supports:

- Blocking communication

- Non-blocking communication

- One-way and two-way data transfer

Common TLM-1 Interfaces

put()get()peek()transport()

We will discuss more about interfaces in next chapters.

Blocking vs Non-Blocking

- Blocking: Caller waits until transaction is completed

- Non-Blocking: Caller continues execution immediately

TLM-1 Port Types

| Port Type | Purpose |

|---|---|

uvm_blocking_put_port | Blocking data transfer |

uvm_nonblocking_put_port | Non-blocking data transfer |

uvm_blocking_get_port | Blocking receive |

uvm_nonblocking_get_port | Non-blocking receive |

uvm_transport_port | Request–response |

Typical Usage:

Sequencer → Driver

Driver → Sequencer (response)

What is TLM-2 in UVM?

TLM-2 is a more advanced and standardized transaction modeling approach, inspired by SystemC TLM-2.0.

It is mainly used for:

- High-level modeling

- Memory-mapped transactions

- Timing-accurate communication

Note: In pure UVM testbenches, TLM-1 is used far more frequently than TLM-2.

Key Features of TLM-2

- Standard transaction payload

- Timing annotation support

- Loosely-timed and approximately-timed models

- Better suited for system-level modeling

TLM-2 Interfaces

| Interface | Purpose |

|---|---|

b_transport() | Blocking transport |

nb_transport_fw() | Non-blocking forward path |

nb_transport_bw() | Non-blocking backward path |

TLM-2 Port Types in UVM

- uvm_tlm_b_initiator_socket

- uvm_tlm_b_target_socket

- uvm_tlm_nb_initiator_socket

- uvm_tlm_nb_target_socket

Industry usage: TLM-2 is more common in virtual platforms and architectural models than in pure UVM testbenches.