The UVM Register Abstraction Layer (RAL) is a critical component of the Universal Verification Methodology (UVM) that simplifies the verification of register-based designs. It provides a structured way to define, access, and manipulate registers and memories in a testbench, ensuring a consistent and reusable approach for verification.

The UVM Register Abstraction Layer (RAL) automates register verification by:

- Providing a high-level object-oriented representation of registers.

- Offering built-in register access methods (read, write, mirror, etc.).

- Supporting automated backdoor and frontdoor access to registers.

- Allowing easy integration with stimulus and checkers in a UVM testbench.

With UVM RAL, verification engineers can interact with registers at a higher level without worrying about low-level details like bus protocols and direct transactions. UVM RAL is not mandatory to use, but it does the job efficiently.

Using UVM RAL offers several advantages:

- Abstraction: The register model abstracts low-level read/write operations, allowing users to perform register accesses without worrying about bus protocols or interface details.

- Automation: The RAL model can automatically generate register access sequences, reducing manual coding effort.

- Consistency: By using a unified framework, the RAL model ensures consistent behavior across the testbench, reducing errors related to manual register handling.

- Traceability: The RAL framework provides a clear mechanism to track register access, making it easier to debug and analyze test results.

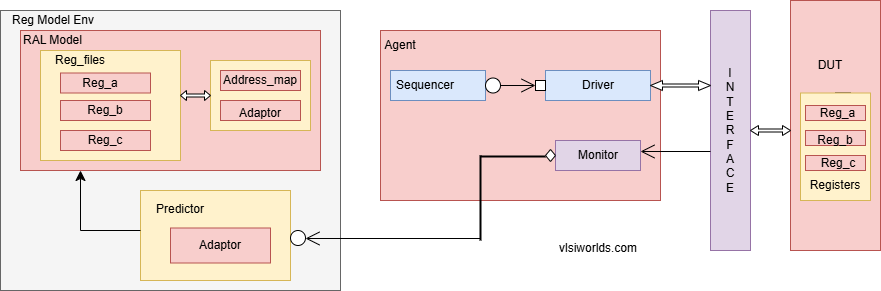

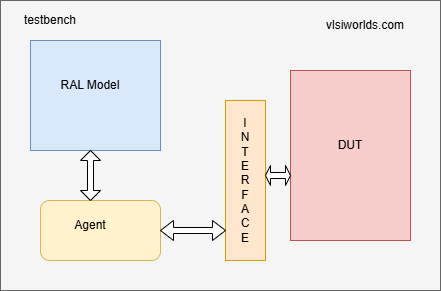

RAL Model Testbench Environment: